Эта статья едва ли для широкого круга читателей, но будет небезынтересна тем, кто хотел бы знать, сколько максимум пакет может полежать где-нибудь в сети, добираясь от точки А к точке Б, и как выбрать коммутатор так, чтобы через месяц от него не тянуло протухшими пакетами.

Для примера — на некоторых современных коммутаторах буферы по 4 гигабайта — спокойно можно четвёртый сезон Рика и Морти сохранить. Или вообще собрать кластер распределённого хранилища из коммутаторов. Не обошлось и без того, чтобы взглянуть по-новому на путь пакета, на архитектуру чипов и процесс производства.В этой статье будет запредельно много сленга, англицизмов и слов на английском, потому что переводить их на русский неблагодарно, а порой и кощунственно.  Но знаете, какая мысль действительно не даёт мне покоя всю дорогу? Как вся эта сложнейшая конструкция: миллиарды транзисторов, размером около десятка нанометров, напечатанных на пластине размером с большую печеньку, которая полдюжиной тысяч ног припаяна к многослойной плате, напичканной мириадами других микрочипов, сопротивлений и конденсаторов и являющейся частью многоюнитовой модульной коробки, управляемой операционной системой, состоящей из сотен прошивок для разных чипов, инструкций по работе с ними, реализаций стандартизированных и проприетарных протоколов и механизмов поддержания жизнедеятельности многочисленных вентиляторов, блоков питания, линейных карт, фабрик коммутации, интерфейсов, процессоров, памяти — вообще хоть как-то работает, а тем более работает настолько стабильно в течение многих лет.Настоятельно рекомендую ознакомиться с 14-м выпуском СДСМ перед тем, как приступить к чтению.

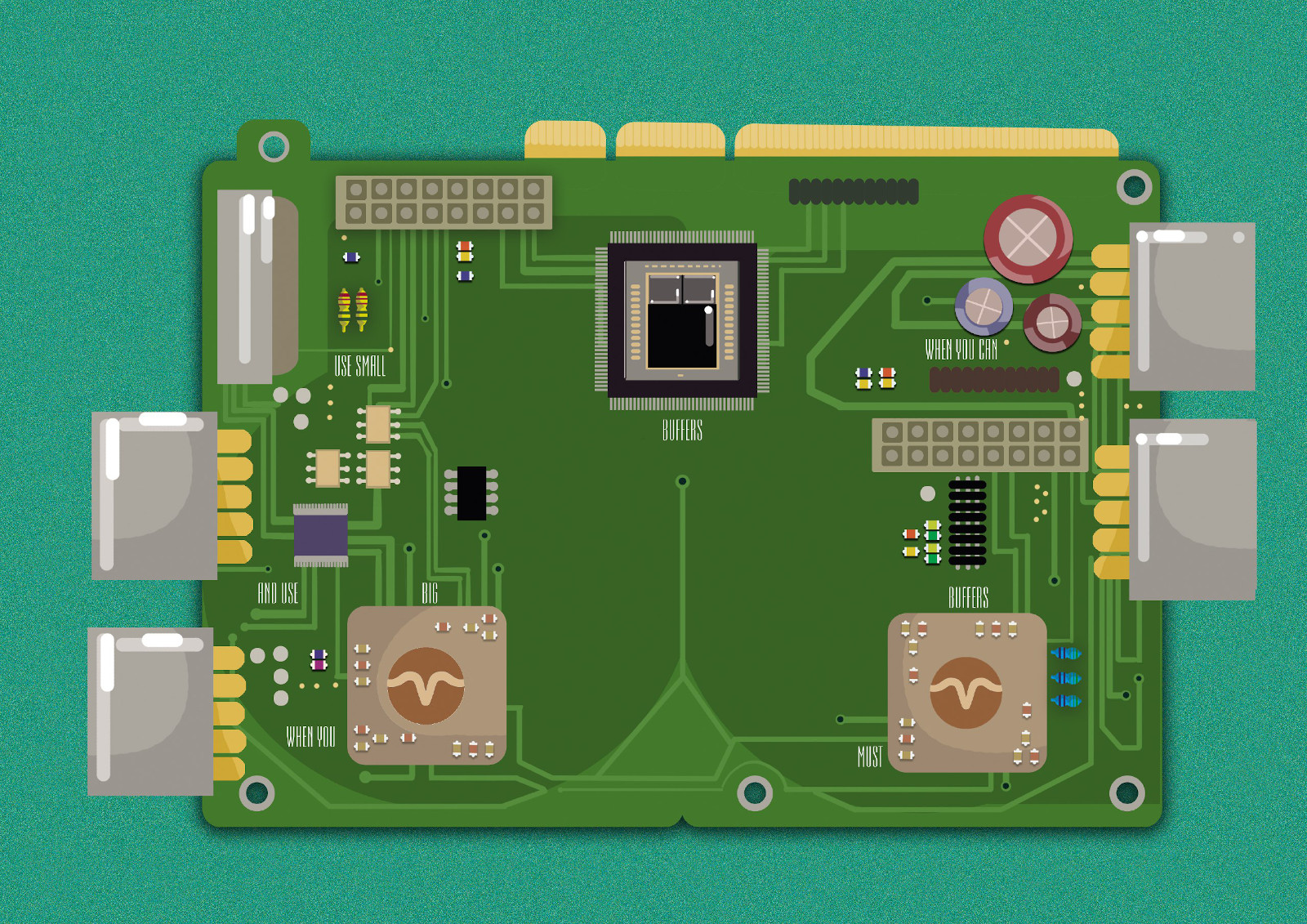

Но знаете, какая мысль действительно не даёт мне покоя всю дорогу? Как вся эта сложнейшая конструкция: миллиарды транзисторов, размером около десятка нанометров, напечатанных на пластине размером с большую печеньку, которая полдюжиной тысяч ног припаяна к многослойной плате, напичканной мириадами других микрочипов, сопротивлений и конденсаторов и являющейся частью многоюнитовой модульной коробки, управляемой операционной системой, состоящей из сотен прошивок для разных чипов, инструкций по работе с ними, реализаций стандартизированных и проприетарных протоколов и механизмов поддержания жизнедеятельности многочисленных вентиляторов, блоков питания, линейных карт, фабрик коммутации, интерфейсов, процессоров, памяти — вообще хоть как-то работает, а тем более работает настолько стабильно в течение многих лет.Настоятельно рекомендую ознакомиться с 14-м выпуском СДСМ перед тем, как приступить к чтению.

Содержание

- Терминология

- Архитектура сетевого устройства

- Типы чипов

- Архитектура ASIC

- Память и буферы

- Lossless Low-Latency сети

- Существующие чипы

- Полезные ссылки

TL;DR

Терминология

Задача этого параграфа не объять все непонятные слова, употребляемые в статье, а лишь внести некую ясность в неразбериху русско-английских терминов.

- Чип коммутации, сетевой процессор, (Packet) Forwarding Engine, PFE — микросхема, способная коммутировать пакет из входа в нужный выход с нужным набором заголовков.

- Pins, пины, ножки — металлические контакты на микросхеме для соединения с основанием.

- Data Path — путь внутри устройства (или чипа), по которому передвигается пользовательский трафик.

- Lookup или лукап или поиск — поиск адресата в таблицах (FIB, LFIB, ARP Adjacencies, IPv6 ND Table итд.)

- Pipeline или конвейер — набор действий, которые происходят с пакетом по мере его продвижения от входа в чип до выхода из него.

- Single-chip, одночиповый — устройство, внутри которого только один чип.

- Fixed, фиксированный, pizza-box — немодульный коммутатор. Обычно внутри него нет фабрик коммутации. Часто эти термины используются как синоним Single-chip, хотя это не совсем верно — внутри может стоять два (back-to-back) чипа или даже больше.

- Сериализация/Десериализация — процесс перевода данных из параллельного низкоскоростного интерфейса (МГц) в

последовательный высокоскоростной (ГГц) и наоборот. Например, из чипа в интерфейс или из чипа в фабрику.

- Память — физическая микросхема для хранения.

- Буфер — некий участок памяти, выделенный для хранения пакетов. Здесь и далее в производных словах, таких как «буферов», ударение на «У».

- Очередь — абстракция над буфером, позволяющая виртуально выстраивать пакеты в упорядоченную очередь. Фактически в памяти они, конечно, хранятся «как попало».

- OCB — On-Chip Buffer — память, встроенная в чип.

- Programmable ASIC — ASIC, логику работы которого можно изменить путём перепрошивки.

- Programmable Pipeline — чип с возможностью для сторонних компаний программировать конкретные части ASIC в ограниченных пределах с помощью предоставляемого вендором компилятора.

- Packaging — упаковка кремниевого кристалла в корпус для предотвращения механических повреждений и коррозии.

- Advanced Packaging — различные технологии, позволяющие внутри одного чипсета компоновать чипы различного вида и назначения. Например, совмещение ASIC и внешней памяти или ASIC и оптического трансивера.

Архитектура сетевых устройств

Итак, что такое сетевое устройство?

Будь то коммутатор, маршрутизатор, файрвол, балансировщик, программный или аппаратный, его задача — доставить пакет со входа на правильный выход, и состоит оно из следующих частей:

Это путь самого пакета.И отдельно от пути пакета — Control Plane Module, который отвечает за то, чтобы путь вообще появился. Это всяческие протоколы маршрутизации, обмена меток и прочее.Это компоненты, которые присутствуют всегда и во всех сетевых устройствах.Реализация же этих функций уже зависит от того, о чём именно мы говорим.

Например, на обычном x86 всю работу, кроме PHY могут взять на себя CPU и оперативка.

Более типично, что функции канального уровня заберёт на себя NIC — Ethernet, проверка контрольных сумм.

А можно в компьютер доставить SmartNIC’и, которые аппаратно могут делать, например, туннелирование.

Но мы не будем сегодня про программные реализации сетевых функций. Поговорим о старых добрых материальных коробках, которым всё равно никуда никогда не деться.

Вообще об этом я уже писал, поэтому повторяться не буду. Точнее буду, но не сильно. Точнее сильно, но я добавлю здесь ещё смысла.Обычно на каждый блок задач выделяется специализированный чип.

Так, всем Control Plane’ом занимаются всё те же CPU + память.

Организация взаимодействия со средой передачи и преобразование битов в сигнал и наоборот — специальные чипы PHY. Почти всегда они реализуются на ASIC.

Разбор заголовков и поиск пути — Packet Forwarding Engine. Это может быть ASIC, Network Processor, реже FPGA и даже CPU. К ним в помощь идёт или обычная память RAM или специальная CAM/TCAM для хранения таблиц лукапа.

Traffic Manager — если вынесен отдельно, то опять же — узкоспециализированные ASIC’и и плюс к ним память. Но может быть встроенным в чип коммутации.Один из вариантов реализации (single-chip устройство):

В этой статье сосредоточимся на PFE и TM, которые и могут вносить вариативные задержки в доставку, потому что могут хранить пакеты.

Типов-Чипов

Было очень страшно начинать эту статью, потому что чипов чудовищное многообразие и простого короткого ответа на вопрос, какой выбрать — нет. Речь и про типы, и про изготовителей, и про серии, и про характеристики.

Ниже я попытаюсь разложить все эти штуки на составляющие детали.

А начнём с типов чипов. Дальнейшая часть этой главы в некоторой степени повторит материал упомянутой выше статьи из цикла СДСМ.

Компромиссы: скорость, функциональность, гибкость, цена

В IT всё есть компромисс. Всегда приходится чем-то жертвовать во благо другого.

Вот классический цискин треугольник про компромиссы:

Здесь не хватает ещё NP и Programmable ASIC. Источник.

Вендоры всегда балансируют в периметре этого треугольника.

Нельзя сделать CPU, проворачивающий через себя 25 Тб/с.

Нельзя сделать универсальный ASIC — зачастую они могут быть аппаратно ограничены по функциям (например, или VXLAN Lookup или IP).

Нельзя сделать дешёвый FPGA.

Кроме того при таком количестве портов, сегодня вступают в игру энергопотребление, место в стойке, тепловыделение и, конечно, цена.

Итак, на сегодняшний день существуют следующие типы чипов, которые могут быть использованы в качестве пакетных процессоров:

CPU

- Неограниченная гибкость

- Неограниченная функциональность

- Приемлемая цена

- Полный провал по производительности

Идея в том, что всё управляется кодом. Инструкции записываются в оперативную память. Для обработки каждого пакета потребуется сходить много раз из CPU в RAM.

С другой стороны для изменения логики работы достаточно переписать программу. Обновления CPU не требуется.

Область применения: домашние и SOHO маршрутизаторы, устройства уровня доступа, файрволы, DPI итд.

Например, абсолютно все рутеры Mikrotik используют CPU для маршрутизации пакетов.

Иными словами CPU годится там, где не гонимся за ультраскоростями, а важен широкий набор функций и невысокая цена.

Впрочем, не без исключений: бывают, что и большие штуки коммутируют в CPU.

Важное замечание: CPU является необходимой частью любого сетевого устройства, потому что берёт на себя задачи Control Plane. А это автоматически означает, что ему придётся работать с протокольным трафиком: OSPF, BGP, LDP, LLDP итд. Кроме того, есть exception трафик — когда у пакета TTL истёк или когда у него стоит бит Router Alert. Ещё CPU нужно самому генерировать трафик тех же протоколов — Self-generated.

Можно ли считать это участием в коммутации? Скорее да, чем нет.

Программная маршрутизация на CPU

Для последнего десятилетия характерна тенденция к маршрутизации в софте. Для всех сетевых функций предлагаются программные альтернативы. Отсюда и DMA, DPDK, VPP, SR-IOV, которые и правда позволяют творить невиданные прежде вещи.

Более того, современные CPU обладают дополнительными блоками инструкций. У Intel это SSE — Streaming SIMD Extensions, позволяющие значительно ускорить обработку трафика.

Тут обычные CPU уже заходят в зону NP (Network Processor) — процессоров, которые можно программировать на языках высокого уровня вроде C, и обладающих большим набором спец. инструкций для работы с сетевым трафиком.

Одним из узких мест современных процессоров ещё является шина доступа — PCIe. В один процессор сейчас более-менее можно загнать 100 с небольшим Гбит/с.

Но как бы производители программных решений ни продвигали идею, что «все можно сделать в софте», однако скорости выше 500 Гбит/с пока что можно достигать только с помощью специализированных асиков.

И давайте ещё прикинем.

Выдержка с сайта про VPP:

Recent testing of FD.io release 17.04 shows impressive gains in performance on Intel’s newest platform when switching and routing layer 2⁄3 traffic. With the prior generation Intel® Xeon® Processor E7-8890v3, FD.io testing showed aggregate forwarding rate of 480 Gbps (200 Mpps) for 4-Socket machine (using 4 of E7-8890v3 CPU configuration); however, the same FD.io tests run on two 2-Socket blades (e.g. a modern 2RU server) with the new Intel® Xeon® Platinum 8168 CPUs (using four of 8168 CPUs in two by two-socket configuration), within the same power budget, show increase of forwarding rate to 948 Gbps (400 Mpps) benefiting from the PCIe bandwidth increase of the new CPUs, and the overall decrease in cycles-per-packet due to CPU micro-architecture improvements.

Xeon E7-8890v3: Рекомендуемая цена $7174.

4 проца по 18 ядер = 72 ядра = 480 Gbps (200 Mpps)

$28696 только за процы

Xeon Platinum 8168. Рекомендуемая цена% $5890.

2 проца по 24 ядра = 48 ядер = 948 Gbps (400 Mpps)

$11780 только за процы

Без обвязки. А ещё кушать электричества он будет как голодный шакал. Не самый дешёвый получится рутер. Зато гибкий.

ASIC

- Околонулевая гибкость

- Ограниченная функциональность

- Низкая цена

- Ультравысокая производительность

Идея в том, что инструкции закодированы аппаратно в виде транзисторов.

Сначала очень долго пишется код, реализующий логику, на специальном языке программирования, вроде Verilog, далее он преобразуется в интегральную схему, отлаживается, проверяется и отправляется в тираж. После этого поменять что-то в логике чипа можно, только произведя новый чип.

Каждый пакет обрабатывается, просто прогоняясь по конвейеру из транзисторов, совершающих заранее определённые действия. Это называется Pipeline.

Область применения: почти любые коммутаторы и многие маршрутизаторы.

Впрочем, не без исключений: Juniper в своей линейке маршрутизаторов MX многие годы использует ASIC Trio.

Вообще по книге об MX: PFE это блок ASIC’ов:

PFEs are made of several ASICs, which may be grouped into four categories:

- Routing ASICs: LU or XL Chips. LU stands for Lookup Unit and XL is a more powerful (X) version.

- Forwarding ASICs: MQ or XM Chips. MQ stands for Memory and Queuing, and XM is a more powerful (X) version.

- Enhanced Class of Service (CoS) ASICs: QX or XQ Chips. Again, XQ is a more powerful version.

- Interface Adaptation ASICs: IX (only on certain low-speed GE MICs) and XF (only on MPC3E)

Речь здесь о классических ASIC — Applicaton Specific Integrated Circuit — статических кусках кремния с аппаратной логикой.

Последние лет 10 в области сетевых микросхем произошёл сдвиг в направлении программируемых ASIC’ов, о которых чуть ниже.

FPGA

Русский термин — ПЛИС — Программируемая Логическая Интегральная Схема.

- Вполне удовлетворительная гибкость

- Вполне удовлетворительная функциональность

- Цена успешного полёта Апполона до Луны и обратно

- Отличная производительность

В отличие от ASIC’ов, где на транзисторах реализованы сами функциональные блоки, в FPGA транзисторами реализуются базовые строительные блоки — регистры, память, LUTы. Из которых потом можно создавать нужные функциональные блоки.

Что это даёт?

А то, что FPGA полностью программируемый — логику работы блоков, из которых он состоит, можно поменять. Для этого потребуется обновить прошивку чипа, что менее удобно, чем загрузить программу в CPU, но гораздо удобнее, чем перепаять ASIC.

Так, если поддержка какой-то функции (условный Geneve) не была заложена изначально, её всегда можно добавить потом новой прошивкой.

Однако за такую программируемость приходится дорого платить.

Область применения: POC или низкоскоростные решения для энтерпрайз-сегмента.

Впрочем, не без исключений: собеседовался я как-то раз в контору, в которой модульную коробку для операторов собирали полностью на FPGA, включая фабрику.

У этого даже есть основания: задолго до появления Programmable ASIC’ов на FPGA можно было делать любую обработку пакетов. И даже через несколько лет после производства плисину легко перепрошить и получить поддержку новой функции.

Автору неизвестны вендоры, которые бы на ПЛИС сделали PFE на скорости более 100 Гбит/с, по всей видимости, потому что частная компания не обладает для этого достаточным капиталом.

Но для рынка энтерпрайз такие решения могут вполне подойти.

Однако, я слышал, что в процессе разработки ASIC возможен такой подход, когда сначала разрабатывается FPGA, программируется нужным образом, тестируется, а потом с неё делают слепок для производства ASIC. Но пруфов нет.

NP — Network Processor

- Отличная гибкость

- Отличная функциональность

- Цена весьма высокая

- Производительность весьма высокая

NP или NPU — Network Processor Unit.

Идея в том, что это почти CPU, который однако заточен под сетевые задачи и изготавливается специально под них.

Он, как и CPU, обычно состоит из нескольких ядер, каждое из которых отвечает за свой сегмент. Для изменения логики так же достаточно переписать код приложения.

NP позволяет делать более сложные штуки — например выполнять циклы (чего лишены ASIC и FPGA), делать NAT, почти любые инкапсуляции, пушить и попать условно произвольное число меток итд.

Долгое время NP позиционировался, как серебряная пуля для всех сетевых приложений.

Но производительность уступает ASIC’ам и FPGA.

Большим преимуществом является то, что писать программы для NP можно на С. Это значительно ускоряет процесс, кроме того, где-то можно переиспользовать код.

Область применения: маршрутизаторы агрегации и ядра.

Впрочем, не без исключений: например Smart-NIC Netronome в начале своего пути использовал Intel IXP.

Programmable ASIC

- Приемлемая гибкость

- Ограниченная функциональность

- Низкая цена

- Ультравысокая производительность.

А вот это уже настоящая серебряная пуля последнего десятилетия.

«Почему бы нам не взять ASIC и сделать его немножечко программируемым?» — таким вопросом, видимо, задались разработчики и выдали замечательную вещь, которую циска в своём треугольнике поместила в самую середину, хотя это и не совсем так, потому что производительность программируемого ASIC’а такая же, как и у обычного. Им удалось вырваться из 2D.

Область применения: коммутаторы, маршрутизаторы.

Большинство датацентровых коммутаторов и некоторые маршрутизаторы уровня границы ДЦ работают на программируемых асиках.

Чипы для датацентровых коммутаторов

Чтобы упростить себе жизнь, я продолжу далее разговор только об ASIC’ах под датацентровые коммутаторы, не пытаясь обнять Джабба Хатта.

До недавних пор на этой ниве пахал только Broadcom со своей оружейной палатой: Tomahawk и Trident — и израильскими городами: Qumran, Jericho итд.

Выбор — особо не разбежишься — ну или разрабатывать своё (как делают Huawei, Juniper и Cisco)

Сегодня конкуренцию ему пытаются составить Mellanox со своими собственными чипами Spectrum (ныне уже Nvidia), Innovium Teralynx, Barefoot Tophino (ныне Intel). Своим появлением эти компании раскачивают рынок и провоцируют среди вендоров тренд на переход от внутренних разработок к готовым чипам их производства.

Мы в конце статьи взглянем на их модельные ряды, но пока давайте обсудим, чем же чипы характеризуются и могут отличаться друг от друга.

А для этого надо понять, какие они задачи решают.

В датацентровых сетях есть три основных типа устройств:

Spine — сравнительно простая железка, требующая самый минимум функций — её задача просто молотить трафик. Очень много и очень быстро. Зачастую это просто IP-маршрутизация. Но бывают и топологии, в которых Spine играет чуть более важную роль (VXLAN anycast gateway). Но обычная практика — держать конфигурацию спайнов максимально простой.

Leaf — чуть более требователен к функциям. Может терминировать на себе VXLAN или другие оверлеи. Здесь могут реализовываться политики QoS и ACL. Зато не нужна такая большая пропускная способность, как для спайнов. Кроме того, в некоторых сценариях (VXLAN) leaf знает о сервисах за подключенными машинами (клиентских сетях, контейнерах), соответственно, ему нужно больше ресурсов FIB для хранения этой информации.

Edge-leaf — это устройства границы сети ДЦ и здесь уже фантазия ограничивается только свободой мысли сетевых архитекторов — MPLS, RSVP-TE, Segment Routing, всевозможные VPN’ы. При этом наименее требовательны к производительности.

На каждом устройстве, соответственно, разные требования к возможностям чипов — как по пропускной способности, так и по набору функций и по количеству ресурсов для хранения чего-либо.

И надо сказать, вендоры чипов и железа добились тут поразительных успехов.

Типичный спайн сегодня — это 64-128 100GE портов на 2-4 юнита с энергопотреблением около 400 Вт. И ценой порядка пары десятков тысяч долларов.

Производителям чипов приходится нелегко не только из-за попыток найти золотую середину, но и из-за возрастающих скоростей передачи данных и конкуренции.

Средняя скорость аплинков с торов сегодня 200-800 Гб/с. Чтобы собрать минимально рабочую сеть ДЦ, нужны спайны с пропускной способностью 3,2 Тб/с.

Всё более и более производительные чипы нужно выпускать уже примерно каждые полтора-два года.

Актуализированная мной картинка из видео PP.

Конкурирующие производители чипов идут ноздря в ноздрю — почти одновременно у всех (Broadcom, Mellanox, Innovium, Barefoot) выходят микросхемы с почти идентичными характеристиками, а вслед за ними и коммутаторы с ними.

Ещё одним компромиссным вопросом является размер буфера, но об этом мы поговорим попозже.

Помимо скорости и обязательных функций по маршрутизации и оверлеям, есть ещё много менее заметных вещей, которые ожидают потребители.

Мы про них говорить сегодня не будем, но не упомянуть было бы ошибкой.

Это, например, телеметрия в реальном времени: наблюдать за утилизацией буферов, видеть бёрсты, дампы отброшенных пакетов, профиль трафика по размерам и типам пакетов.

Кроме того, сегодня набирает популярность INT — Inband Network Telemetry.

Для многих незаметно, но уже почти жизненно важно, начинает работать динамическая балансировка трафика: чип отслеживает потоки (flows) и дробит их на флоулеты (flowlets) — короткие куски трафика одного потока, разделённые между собой паузой в несколько миллисекунд. Эти флоулеты он может динамически распределять по разным путям (ECMP или членам LAG), чтобы обеспечить более равномерную балансировку. Особенно важно это для Elephant Flows, оккупирующих один интерфейс.

Пользователям всё чаще хочется иметь возможность управлять распределением буфера, ну а перераспределение ресурсов FIB — это уже функциональность, отсутствие которой будет вызывать вопросы.

В условиях датацентров ECMP и балансировка силами сети — это воздух, вендорам нужно обеспечить нужное количество как ECMP-групп, так и общее количество Next-hop’ов.

Поэтому нет одного чипа или тем более SoC, решающего сразу все задачи.

Под каждую роль разработаны свои чипы. Одни из них ориентированы на пропускную способность, другие на широкую функциональность, третьи на низкие задержки.

Посочувствуем же бедным вендорам и будем выбирать долларом.

Архитектура сетевых ASIC

Сначала мы взглянем на физиологию чипа — из каких компонентов он состоит.

А далее разберёмся что с пакетом в этих компонентах происходит.

Физическое устройство

Итак, для успешной коммутации пакета нужны следующие блоки:

- Парсер заголовков (Parser)

- Лукап (Match): FIB/LFIB, Nexthop-группы, ARP Adjacencies, IPv6 ND Tables, ACL итд

- Блоки преобразований (Action)

- Блок управления памятью (TM/MMU)

- Сборщик пакета (Deparser)

- SerDes

- Память для буферизации пакетов

- Блок, реализующий MAC

- Чип PHY

- Физические порты/трансиверы

Крупными мазками: оптический или электрический сигнал попадает на порт (Rx), тот его передаёт на PHY. Модуль PHY реализует функции физического уровня и передаёт биты на входные пины PFE, где сигнал блоками SerDes преобразуется в удобоваримый для чипа вид. Блок MAC из потока битов восстанавливает Ethernet-кадр и передаёт его парсеру. Парсер отделяет необходимые ему заголовки и передаёт их на анализ следующему блоку Match/Action. Тот их исследует и применяет нужные действия — отправить на правильный порт, на CPU, энкапсулировать, дропнуть итд. Тело пакета всё это время хранилось в буферах, управляемых MMU, и теперь пришло время Traffic Manager’у проводить все обряды QoS. И потом процесс раскручивается в обратную сторону. Снова Match/Action. Потом собрать пакет с новыми заголовками (Deparser), преобразовать кадр в поток битов (MAC), сериализовать (SerDes), осуществить действия физического уровня (PHY) и передать через выходной порт (Tx) в среду.

В простейшем случае вообще почти все блоки являются частью одного монолитного кристалла кремния. То есть они — продукт одного процесса печати на вафле.

Отдельные, составляющие чип компоненты, реализующие законченный набор функций, называются IP-core (не тот, что ты мог подумать, сетевой инженер!). То есть SerDes, MAC, TM — это всё отдельные IP-core. Зачастую они производятся сторонними компаниями, специализирующимися конкретно на данных компонентах, а потом встраиваются в микросхему. Особенно это касается SerDes — сложнейшей детали, в которую вендоры сетевых чипов не готовы вкладывать силы R&D. Один из крупных производителей SerDes — Inphi.

Монолитный чип Rosetta. Источник.

Другой распространённый вариант: в одном чипе сочетать несколько разных кристаллов с интерконнектом между ними.

Так, например, off-chip память HBM коммерческого производства выносится за пределы кристалла сетевого ASIC:

Под крышкой одного производительного чипа могут быть собраны несколько, так называемых, менее производительных чиплетов (chiplet), которые, объединённые в фабрику, дают бо́льшую пропускную способность:

Для некоторых решений рядовая практика — вообще все ресурсы выносить за пределы сетевого ASIC’а:

В случае Juniper, кстати, их Trio — это не один ASIC — это их набор, каждый из которого реализует свои функции.

Но как бы ни был устроен сам чип, ему нужно общаться с миром.

И поэтому на животике у него есть несколько тысяч пинов:

Одни пины нужны для того, чтобы подключить к чипу интерфейсы.

Другие — чтобы подключиться к внешней памяти (CAM/TCAM/RAM), если она есть.

Третьи — к фабрике коммутации, если коробка модульная.

Два пина образуют дифференциальную пару для передачи данных в одном направлении. То есть две пары пинов нужны для полнодуплексной передачи.

Вот так оно потом выглядит в программах для проектирования (для случая на порядок более простой микросхемы):

Теперь пришло время разобраться с тем, что же такое загадочный SerDes. Нет, это не ножки на микросхеме.

SerDes

Если коротко — то это блоки (IP-core) сетевого ASIC’а, которые позволяют получить сигнал с пинов и, наоборот, передать его туда.

Теперь с этимологией. Аналогично «модему» и «кодеку», ставшим уже такими родными в кириллическом написании, SerDes составлен из двух слов: Serializer-Deserializer. Так чего же он сериализует и десериализует?

Всё дело в скорости работы сетевых чипов. Независимо от их типа (ASIC, NP, CPU) — их частота находится в пределах сотен Мгц — единиц Ггц. А частота передачи данных с порта 10Гб/с — 10 Ггц (100 Гбит/с = 4х25ГГц). Соответственно, каким-то образом нужно понизить частоту внутри чипа. И как раз это достигается тем, что сигнал из пары вводных пинов распараллеливается на множество внутренних линий — десериализуется.

В обратную сторону — сигнал с нескольких линий нужно сериализовать в пару пинов.

Блоки SerDes всегда являются составными частями кристалла сетевого чипа.

Один SerDes — это 4 пина на пузике асика — два для Tx, два для Rx.

Скорость одного SerDes’а — величина скачкообразно растущая с годами. Наиболее распространённые сегодня — это 10Гб/с и 28Гб/с. Но в скором будущем датацентровый масс-маркет начнут заполонять устройства с 56Гб/с SerDes и даже со 112Гб/с.

Выглядит довольно сложным. Для чего же вообще устраивать эту сериальную вакханалию, а не сделать просто пинов по числу реальных линий в чипе?

Зачем?

Ну, давайте прикинем, спайн-коммутатор с 64х100Гб/с портами несёт под кожухом ASIC ёмкостью 6,4 Тб/с.

Если каждые 4 пина чипа могут обеспечить 28Гб/с в полном дуплексе, значит, на нём должно быть 64*4*4=1024 пинов.

Это уже как минимум 32х32 пинов на 40 см^2, не считая питания и земли. И они там сидят довольно плотненько. Легко ли будет кратно нарастить их количество?

Однако проблема не только и не столько с количеством пинов.

Тенденция к серийным интерфейсам намечается уже давно.

На смену периферийным параллельным портам пришли серийные (USB на смену параллельному)

На смену IDE — SATA (Serial ATA)

На смену SCSI — SAS (Serial SCSI)

На смену PCI — PCI Express

Это жжж неспроста. Ведь казалось бы, чем больше проводов, тем больше данных можно передать за единицу времени?

На самом деле нет — при параллельной передаче с повышением скорости всё острее и острее встают вопросы синхронизации между этими самым проводами. Схемотехники даже связанные дорожки на платах проектируют так, чтобы они были максимально одинаковой длины.

В какой-то момент задача усложнилась настолько, что дальнейшее развитие пошло по увеличению полосы пропускания обычной дифф-пары вместо параллелизма. В частности для 100Гб/с другого варианта просто не существует.

Модуляция

То, каким образом множество параллельных сигналов укладывается в один, зависит от метода модуляции.

Для SerDes с пропускной сопособностью 10Гб/с и 28Гб/с используется NRZ — Non-Return-to-Zero.

С ним же добились и 56Гб/с. Но всё же стандартом de facto для 56Гб/с и de iure для 112Гб/с является PAM4 — 4 -level Pulse Amplitude Modulation.

Есть и ленивые пессимистичные взгляды в сторону PAM8.

Итого, учитывая современные реалии (NRZ), для того, чтобы запитать данными интерфейс 100Гб/с нужно подвести к нему 4 SerDes’а по 28Гб/с (или 16 дорожек). Отсюда и берётся «лейновость» 100Ж-портов: 4 лейна — это 4 канала по 28Гб/с.

И это то, что позволяет 1х100Ж порт разбить на 4х25Ж с помощью гидры.

В случае PAM4 для 100Ж нужно только 2 SerDes’а по 56Гб/с, то есть два лейна.

GearBox’ы

Сложности с переходом на новые методы модуляции заключаются в том, что устройства на разных сторонах должны использовать одинаковые, либо нужно ставить дополнительные конвертеры. То есть просто подключить сотками коммутатор с PAM4 к NRZ не получится.

Но когда индустрия бросала своих участников, не предлагая им решений? Для того, чтобы устройства с разными модуляциями могли взаимодействовать друг с другом, изобрели коробки передач, которые из малого количество высокоскоростных линий делают много помедленнее и наоборот.

Так, в новейшие коммутаторы, выпускаемые сегодня, ставят дополнительные чипы, чтобы их можно было использовать в сети с более старым оборудованием.

Использование гирбоксов также упростит вендорам и переход на 400G — не придётся менять ASIC — достаточно заменить/убрать гирбокс.

PHY

Этот зверь тоже по-своему интересен.

Его задачи незамысловаты:

- Конвертация сигнала между средами (оптика-медь), если это нужно

- Восстановление битов из сигналов и наоборот

- Коррекция ошибок

- Синхронизация

- И другие задачи физического уровня.

Если хочется знать больше, и не пугают забористые тексты со страшными картинками: PHY Interface for PCI Express, SATA, USB 3.1, DisplayPort, and Converged IO Architectures.

Что действительно любопытно и достойно обсуждения — так это его расположение.

Если порт медный — RJ45, то чип PHY — это ASIC, установленный на плате.

Если порт оптический, то в подавляющем большинстве случаев эти функции возьмёт на себя DSP PHY, встроенный в трансивер (та самая штука, называемая нами модулем и вставляемая в дырку в коммутаторе).

Однако тенденции последних лет — это Silicon Photonics.

Самый производительный коммерческий чип сегодня выдаёт 25,6 Тб/с. Это серьёзнейший инженерный вызов разработчикам. И нет никаких оснований полагать, что гиперскейлеры и экзаскейлеры умерят свои аппетиты и решат остановиться на этом. Скорость будет расти.

Чип PHY находится на трансиверах, а SerDes — на кристалле сетевой микросхемы. Сигнал между ними идёт по электропроводящей среде — по металлической дорожке. С увеличением скоростей растёт и конструктивная сложность и потребляемое электричество. Рано или поздно (скорее, рано) мы во что-нибудь упрёмся.

В случае silicon photonics микросхема PHY переносится внутрь самого чипа коммутации. В кристалл «встраиваются» фотонные порты, позволяющие осуществлять коммуникации между чипами на скорости света через оптическую среду.

Идея не новая, и только ожидавшая своего времени, а именно, когда технологии достигнут нужного уровня зрелости.

Проблема была в том, что материалы и процессы, используемые для производства фотонных чипов, были фундаментально несовместимы с процессом производства кремниевых чипов — CMOS.

Из возможных альтернативных решений: установка на плату отдельного чипа, преобразующего электрический сигнал в оптический, или его установка внутрь сетевого чипа, но не на сам кристалл (всё ещё требует конвертации среды).

Но эта технологическая плотина смыта упорными разработками в этом направлении, и в скором будущем микроэлектронику ждут большие изменения.

Весьма занимательная статья с историей вопроса и сегодняшними реалиями.

Кстати, был у нас в гостях Compass EOS, которые разработали co-packaged optics ещё до того, как это стало модным. Но, увы, они настолько опередили своё время, что оказались в тот момент никому не нужны. И постигла их ужасающе печальная судьба быть купленным не то Ростелекомом, не то Роснано. Впрочем, возможно, история звучала совсем иначе :).

И прямо во время написания этой статьи 5-го марта 2х20 Intel опубликовал в своём блоге новость о том, что они продемонстрировали первый свитч, в котором им удалось интегрировать свой интеловский silicon photonics в барефутовский Tofino2.

Напоследок хочется немного времени посвятить прям совсем кишочкам, скрытым под металлической крышкой.

Packaging и Advanced Packaging

Packaging (корпусирование) — это процесс упаковки кристалла в корпус, который защитит его от физических повреждений и коррозии.

Корпусированный набор чипов. Источник.

Я честно предпринял попытку разобраться в этом вопросе, но уже на втором часе чтения стало понятно, что, если хоть немного глубже общих понятий погружаться, то это будет требовать ещё одной статьи такого же размера, чтобы не прослыть дилетантом.

Когда-то давно, внутри одной микросхемы на плате был один кристалл.

Даже не так — когда-то давно в микросхеме было несколько полупроводниковых элементов.

Прототип первой интегральной схемы. Джэк Килби. Источник.

Нужно две микросхемы — ставим их рядом, соединяем дорожками.

Нужно много-много микросхем — делаем большие платы или собираем платы в несколько слоёв.

Со временем транзисторы становились меньше, а микросхемы сложнее — внутри одного кристалла могли совмещаться несколько логических блоков — это были первые SoC — System On Chip — ЦПУ+Память+какие-нибудь специфические задачи. Но сильно много туда всё равно не засунешь.

SoC Apple A6. Источник.

Потом научились, нарезав вафли на отдельные кристаллы, каждый из них запаковывать в отдельный пластиковый пакет, ставить один на другой и корпусировать вместе.

Толщина таких бутербродов получалась большой — заметно больше, чем толщина ядра.

Что сделало возможными семимиллиметровые телефоны — так это Wafer-Level Packaging (WLP) или ещё это называют Advanced Packaging — технологии, позволяющие на одной вафле делать несколько микросхем и связывать их друг с другом.

Сюда относятся: 2D, 2.5D, 3D, Fan-Out, 2.1D итд.

Неполное многообразие способов компоновки. Источник.

Каждый отдельный чип называется чиплетом (chiplet).

Отличаются технологии Advanced Packaging’а друг от друга расположением чиплетов (рядом или один на другом), наличием и отсутствием интерпозера, материалом интерпозера (кремний, стекло, органика), видом электрических связей между кристаллами (металлические дорожки или TSV) и массой других.

Суть их всех в том, что такая более плотная компоновка позволяет уменьшить размер, увеличить количество шин передачи данных, а соответственно и пропускную способность, значительно сократить энергопотребление и тепловыделение, отказавшись от длинных металлических дорожек.

Зачем я вообще в это решил копнуть? Во-первых, теперь немного понятнее становится что такое co-packged optics из предыдущего параграфа — это чиплет, реализующий оптический интерфейс, упакованный по одной из этих схем внутрь чипсета с ASIC’ом.

А, во-вторых, дальше я буду рассказывать о памяти и буферах. Также я скажу о том, что каждый коммутационный ASIC обладает небольшим объёмом встроенной памяти — On-Chip Buffer.

Она является составной частью асика коммутации.

Однако в некоторых случаях в помощь к ней добавляют объёмную внешнюю память, в которой пакеты будут храниться, если они не помещаются во встроенную. И пока это была какая-нибудь GDDR5, вынесенная отдельно на печатной плате в виде самостоятельного чипа, всё было понятно.

Своего родного сетевого не нашлось, но вот тут карточка от Энвидии с вынесенными GDDR5.

Но сегодня, с появлением WLP, когда под одной крышкой собраны и логика и память, границы начинают размываться. Некоторые вендоры спекулируют тем, что внешняя память co-packaged с коммутационным ASIC’ом, и утверждают, что она On-Chip.

Так, например, выглядит 2.5D корпусирование, где один чиплет соединён с другим через кремниевый интерпозер:

2.5D — это развитие классического подхода 2D. Оно всё ещё требует дорогостоящего выхода за пределы чиплета и прохода по длинным металлическим дорожкам. И кроме того обладает сравнительно невысокой пропускной способностью, ограничивающей максимальную скорость, на которой может работать чип в условиях, близких к перегрузкам.

Другой вариант — это уже 3D WLP:

Ну красивая же картинка? Я просто не удержался от того, чтобы вставить её. Источник.

Вот «более настоящая» схема устройства чипа Broadcom Jericho2. Здесь несколько чиплетов памяти HBM стекированы один на другой по технологии 3D, а сам чип коммутации с этим блоком внешней памяти взаимодействует через интерпозер.

А вот совсем уж настоящее фото чипсета Juniper ZX EXPRESS, совмещающего память и ASIC под одной крышкой:

HBM — High Bandwidth Memory — как раз и является High Bandwidth благодаря очень широким шинам взаимодействия между плотно скомпонованными чиплетами.

Расположенные друг над другом они соединены через TSV — Through-Silicon Via — это микроскопические проходные отверстия в кристаллах, залитые металлом (например, вольфрамом), которые позволяют чипам общаться друг с другом. Они значительно короче линий в интерпозере, что позволяет их сделать гораздо более эффективными.

TSV. Источник.

HBM весьма уверенно пробивает себе дорогу сегодня в мир Deep-Buffer коробок.

Кстати по такой же 3D-технологии корпусирования была создана память HMC — Hybrid Memory Cube. Это бутерброд из склеенных друг с другом плашек DRAM, пронизанных TSV.

HMC — это коммерческая память производства Micron, от которой ныне отказались в пользу HBM и GDDR6.

Считать ли такую компоновку действительно On-Chip или нет — вопрос открытый, но складывается мнение, что в будущем необходимая от ASIC’а скорость коммутации будет расти всё равно быстрее, чем пропускная способность интерфейса до пусть даже лежащего плотно на ней чиплета HBM.

В чуть более узком, коммутационном смысле, под чиплетами могут иметься в виду составные части сетевых чипсетов, в которых высокая пропускная способность достигается не более производительным кристаллом, а набором нескольких менее производительных чиплетов, соединённых друг с другом через внутреннюю фабрику.

Бродком, кажется, считает это малодушием, продолжая изготавливать свои ультра-производительные чипы на монолитном кристалле.

Дальнейшее чтиво:

- Understanding chiplet in one article

- Advanced packaging: five trends to watch in 2017

- Fan Out – Simple to Complex

Теперь от вещей мирских к тому, сколько кругов пакет проходит в чипе.

Логическое устройство

Типичный сетевой ASIC представляет из себя конвейер, по которому пакет передаётся от входного интерфейса к выходному, а по пути с ним случаются приключения. Английский термин для этого — Pipeline.

Хотя с виду и не скажешь:

В самом общем виде Pipeline выглядит так:

Пакет проходит через все стадии как минимум один раз, но для реализации сложных действий, вроде дополнительной инкапсуляции (VXLAN), может отправиться повторно.

Parser

Сначала на вход попадает пакет с неизвестным набором заголовков.

Парсер разбирает все заголовки, отделяя их от собственно данных.

Если это L2-коммутатор, то его заинтересует только заголовки Ethernet и VLAN.

Если это MPLS-коммутатор, он заглянет в MPLS заголовки.

Для L3 соответственно IPv4 и IPv6.

Если это VXLAN-терминатор, ему понадобится UDP и собственно заголовок VXLAN.

Для целей ECMP и ACL, парсер заглянет в UDP/TCP.

Строго говоря, на какие заголовки и какие поля в них надо смотреть, определяет фантазия разработчика.

Сколько заголовков забрать? Как правило парсер вынимает фиксированное для чипа значение байтов от пакета и разделывает уже их. И это значение является одним из ограничений чипа.

Почему парсинг заголовков задача нетривиальная рассказывается в совместном исследовании Стэнфорда и Майкрософта: Design Principles for Packet Parsers.

Pre-Ingress processing

Иногда логически выделяют этот блок, который совершает действия, не являющиеся ни парсингом, ни как таковым лукапом — он кладет пакет в нужный VRF, ставит внутренний Traffic Class итд.

Ingress Match-Action

Когда парсер, разобрался с чем он имеет дело, он передаёт заголовки дальше — в модули Match-Action.

Здесь происходит lookup. Для L2 поищем MAC’и, для L3 — прошерстим FIB, для MPLS — просмотрим в LFIB.

И здесь же принимается решение, что с пакетом делать дальше: доложить CPU, пропустить/дропнуть, побалансировать, в какой порт отправить, какие заголовки навесить, с каким приоритетом внутри чипа обработать, полисить ли/шейпить ли его итд.

Собственно действие записано в той же таблице, в которой происходит lookup.

Это если коротко.

А если чуть подлиннее, то:

L2 short pipeline

Приходящий L2-пакет всегда ассоциируется с VLAN. Тег VLAN проверяется через VLAN Lookup Table.

Если VLAN lookup успешен, просматриваются таблицы: VLAN STP, VLAN Port Bitmap, Port Filtering Mode (PFM).

Если же тег неверный, то пакет сбрасывается (или нет).

После пакет проходит стандартную обработку: запомнить SRC MAC, посмотреть в таблице DST MAC, — но при этом могут быть применены дополнительные флаги, например, отправить на CPU unknown sender.

L3 short pipeline

Если DST MAC является MAC’ом самого устройства, то процессинг передается в L3 модуль.

Следующий шаг — Destination Lookup. Сначала используется L3 Table Lookup, в этой таблице как правило directly attached хосты.

Если адрес найден, то выдается index в L3 Interface Table, в котором выходной порт, MAC, VLAN.

Если же в L3 table не найден адрес, то делается LPM поиск (Longest Prefix Match). Результат такого поиска — index в L3 Table Lookup таблице, который должен использоваться для форвардинга. После удачного поиска, чип поменяет SA/DA/VID пакета (L2), посчитает FCS, поменяет TTL и IP checksum.

Traffic Manager + MMU

Может также называться Buffer Manager.

В этом блоке происходят следующие операции:

- Постановка пакетов в очередь

- Их хранение (буферизация)

- Контроль перегрузок

- Диспетчеризация

- Репликация

Он состоит из двух частей — MMU и TM. Первый отвечает за управление памятью и буферами, второй — за QoS и мультикаст.

MMU — Memory Management Unit — компонент чипа, который управляет физической памятью.

Одна из его функций аналогична MMU (блоку управления памятью) обычного компьютера — доступ приложений к физической памяти и её защита.

Но список его обязанностей гораздо шире, поскольку заточен он на работу именно с пакетами. Он отслеживает как память распределяется между интерфейсами и насколько она занята в каждый момент времени, можно ли поместить пакет в буфер, если да, то в какой, как разбить его на более мелкие ячейки, ну и, конечно, как его оттуда забрать.

TM — Traffic Manager — решает более высокоуровневые задачи — выделение очередей, помещение в них трафика, диспетчеризация, шейпинг, полисинг, управление перегрузками. В общем, всё, что относится к QoS, а так же к мультикасту.

С мультикастом история, право, интересная (как всегда). Репликацией мультикастовых пакетов занимается блок TM. В модульных устройствах это происходит в два этапа: сначала на входном чипе создаётся столько копий, сколько выходных чипов должны получить этот пакет, а затем на выходных чипах ещё столько копий, сколько портов на этой плате должны его получить. Делается это для того, чтобы лишними копиями не загружать фабрику.

Любопытный момент с буферизацией и контролем перегрузок: входной чип должен учитывать занятость выходного порта, прежде, чем отправлять пакет, потому что именно входная плата управляет VOQ. Поскольку Traffic Manager оперирует не самими пакетами, а по сути информацией о них, то ему необязательно делать сразу копий по числу выходных портов, а достаточно записать об этом информацию в VOQ.

MMU — это не совсем часть TM — это, скорее, два взаимодействующих друг с другом блока.

Память и буферизация на сетевых устройствах — это настолько масштабная тема, что ей я посвятил отдельную статью, которая выйдет на nag.ru прямо следом за этой. В ней мы разберёмся с устройством и архитектурой памяти, видами и расположением буферов, арбитражем и поднимем самый горячий вопрос современности — что лучше: большие и маленькие буферы.

В разговорах о буферах связка TM+MMU — одни из важнейших блоков ASIC’а (или внешний чип), поэтому к ним мы ещё вернёмся ниже.

Egress Match-Action

Далее над заголовками пакетов могут быть совершены дополнительные акты — например, выходной ACL, туннельные инкапсуляции, сбор статистики итд.

Deparser

К этому моменту на основе результатов обработки в блоках Match-Action сформирован список новых заголовков, и он может воссоединиться с телом пакета.

Сам пакет теперь готов в последний путь внутри этого чипа, чтобы выйти через выходной интерфейс.

Кроме того, здесь может собираться дополнительная статистика о длине пакетов и сообщаться блоку TM и зеркалироваться исходящий трафик.

Вышеуказанные стадии могут быть выполнены в пределах одного чипа, а могут быть и разнесены на разные.

Так, в случае single-chip-коробки — все они скомпонованы в один кусочек силикона, площадью с фотку на документы.

На модульных коробках Parser и Ingress Match-Action — это входной чип коммутации, Egress Match-Action и Deparser — выходной, TM стоит отдельно между чипом коммутации и фабрикой, и может быть разделён на Ingress и Egress. Кроме того в модульных устройствах могут существовать ещё и отдельные чипы Fabric Interface, которые разбивают пакеты на ячейки одного размера и отправляют в фабрику.

Pipeline

Пайплайном называется весь процесс доставки пакета от парсера до депарсера.

Что хорошо — можно делать несколько Match-Action подряд, например, отлукапив сначала Ethernet, потом IP, потом ещё и TCP для ECMP.

Что плохо — число этих действий строго ограничено — ASIC вещь достаточно детерминированная.

Это ведёт к тому, что некоторые вещи становятся аппаратно невозможны. К примеру, на старых Trident’ах нельзя было сделать и VXLAN и IP lookup последовательно для одного пакета. Или в другой ситуации коробка у меня не могла снять метку, сделать рекурсивный IP-lookup и навесить две новые метки.

Однако у таких трудностей есть как минимум три решения:

1) Второй чип. Тогда можно и разнести невозможные прежде операции на два этапа. И история знает такие решения.

2) Рециркуляция. Многие чипы позволяют закольцевать выход чипа на вход и прогнать пакет дважды. Тогда на второй итерации ему можно задать уже другой набор Match-Action. Но за это придётся заплатить — удвоенной задержкой и уменьшенной полосой пропускания чипа. А ещё можно упереться и в пропускную способность самого рециркулятора.

3) Купить другой чип… Другой коммутатор… Поменять работу…

Programmable Pipeline

В большинстве современных коммутаторов конвейер обработки пакетов запечён производителем в софт (если не в кремний) — он фиксирован и может быть изменён только вендором чипсета.

Не путать с Programmable ASIC. Программируемые микросхемы — уже давно реальность. Многие сетевые чипы — это ASIC с возможность программирования. Но эта возможность есть только у производителя микросхемы.

Программируемый конвейер же — это возможность изменять логику работы чипа в определённых пределах, которую предоставляет производитель микросхемы покупателям.

Не так давно появился Barefoot Tofino, у которого полностью программируемый Pipeline — с ним можно задавать совершенно любые условия для парсера, поля для Match и действия для Action — хоть калькулятор пишите, или распределённое хранилище на кластере коммутаторов.

На сегодняшний день выпускать сетевую микросхему на рынок без возможности программирования Pipeline’а, становиться плохим тоном.

Так, последние чипы Broadcom тоже уже программируемы.

Не то чтобы теперь каждый домовой оператор кинется переписывать себе пайплайны, нанимая студентов для разработки под P4 или NPL, но это возможность, которая позволяет вендорам железа и крупным потребителям вроде гугла быть гораздо более гибкими.

Так, например, если в вашей сети все линки p2p, то зачем вам Ethernet? тратить на него такты ASIC’а ещё — просто выкидываем его.

Правда «можно всё запрограммировать» превращается в наших реалиях «придётся всё запрограммировать». На сегодняшний день готовых конструктивных блоков, вроде парсинга Ethernet, IP, подсчёта статистики итд — не существует — всё с нуля.

Если не использовать вендорские бинари, то весь Pipeline придётся написать самому. А если использовать, то ничего за пределами SDK не запрограммируешь.

Но на большинстве современных коммутаторов всё ещё фиксированный конвейер, который выглядит примерно так:

Дальнейшее чтиво:

Cisco всё ещё делает классную документацию, а презентации с Cisco Live — кладезь технических сокровищ. Например, они рассказывают о бродкомовских чипах больше, чем сам Бродком (если, конечно, вы не подписали NDA кровью): Cisco Nexus 3000 Switch Architecture

Вот у P4 есть неплохое описание конвейера и его программируемости: P4 Tutorial, Hot Chips 2017.

Более фундаментальное и низкоуровневое описание RMT — Reconfigurable Match Tables, необходимых для возможности программирования: Forwarding Metamorphosis: Fast Programmable Match-Action Processing in Hardware for SDN.

Память и буферы

Ну вот мы и добрались до ниточки, с которой клубок начал распутываться.

Всё, что было выше, касалось заголовков пакетов — они отделялись и подвергались алгоритмическим экзекуциям в пайплайне.

А где же прохлаждались их тела всё это время?

В сетевых чипсетах есть встроенная память (OCB — On Chip Buffer) как раз для хранения тел. Её размер в силу физических ограничений очень мал (до 100Мб), но для большинства задач — это разумный компромисс.

Бывают редкие исключения, где встроенная память имеет больший размер.

Но всегда были и будут сценарии, в которых нужна память гораздо большего объёма, в этом случае прибегают к использованию внешней относительно чипа коммутации памяти. Такие устройства называются Deep Buffer.

И о них и вообще о компромиссах мало-много памяти поговорим отдельно.

Таким образом на входе в чип парсер отделяет заголовки от тел, первые отдаёт на анализ в блок Match-Action, вторые — складывает в буфер.

На выходе новые заголовки пришивают к извлечённым обратно телам и отправляют на выход.

Будучи неоднократно обвинённым при рецензировании этой статьи, чувствую необходимость ещё раз повторить это: внутри чипа коммутации заголовки отделяются от тела пакета. В то время, как изначальные заголовки анализируются, помогают сделать лукап, уничтожаются, формируются новые, тело находится в одном месте физической памяти, не перемещаясь. Даже в тот момент, когда Traffic Manager выстраивает пакеты в очередь согласно их приоритетам, производит их диспетчеризацию и Congestion Avoidance, фактически он работает со внутренними временными заголовками, не двигая пакеты по памяти.

Управляет доступом к физической памяти MMU — Memory Management Unit. Он довольно похож на MMU в компьютерах (по сути является им). Программа обращается к указателю, чтобы извлечь данные из памяти, MMU транслирует это в реальный адрес ячейки и возвращает данные.

MMU занимается размещением пакетов в буферах, их извлечением или отбрасыванием. Он же контролирует разделение памяти на области (dedicated, shared, headroom, voq) и их загрузку.

За более верхнеуровневое управление очередями и перегрузками отвечает блок TM — Traffic Manager.

Есть два подхода к размещению тел в буферах: Store-and-Forward и Cut-Through.

Store-and-Forward vs Cut-Through

SF — Store and Forward предполагает, что чип сначала получает полностью пакет, сохраняет в буфере, а уже потом занимается вивисекцией.

После анализа заголовков пакет помещается в правильную выходную очередь.

Исторически это первый метод коммутации. Его преимущество в том, что он может, получив пакет целиком, проверить контрольную сумму и выбросить побитые.

CT — Cut-Through, напротив, сразу после получения первых нескольких десятков байтов пакета, позволяющих принять решение о его судьбе, отправляет его в выходную очередь, не дожидаясь его полной доставки.

Это позволяет сэкономить до нескольких микросекунд на обработке пакета внутри коробки, ценою, однако, отсутствия проверки целостности — ведь FCS-то в конце. Эта задача перекладывается на протоколы более высокого уровня (или на следующий хоп).

Такой режим используется для приложений, требующих ультра-коротких задержек.

К слову на сегодняшний день для коммутаторов 2-го уровня время обработки в пределах устройства порядка 200нс, 3-го — 250нс.

Для коммутаторов 1-го уровня (фактически патч-панель) это время — около 5 нс.

Многие производители сегодня по умолчанию устанавливают режим Cut-Through, поскольку ошибки на Ethernet сегодня явление сравнительно нечастое, а приложение обычно само может обнаружить проблему и запросить переотправку (или не запрашивать, кстати).

Дальнейшее чтение:

Весьма глубокий подкоп под режимы коммутации от циски: Cisco Nexus 5000 Series Switches

Перегрузки: причины и места

Буфер нужен на сетевом устройстве не только для того, чтобы похранить тело пакета, пока его заголовки перевариваются в кишках чипа.

Как минимум нужно сгладить поток пакетов до скорости выходного интерфейса. Грубо говоря, пока один пакет сериализуется для передачи в интерфейс, второму нужно где-то подождать.

Для этой задачи обычно хватит совсем небольшой FIFO очереди.

Другая важнейшая сетевая задача — перегрузки (congestion). Если в один интерфейс одновременно сваливается много пакетов, их тоже нужно сохранить.

Причём перегрузки — это наша повседневная легитимная реальность, а не что-то крайне редкое, что нужно перетерпеть и станет попроще.

Во времена коммутации каналов такой проблемы не стояло — для любой общающейся пары всегда было зарезервировано строго необходимое количество ресурсов.

Сегодня совершенно законно на порт может прийти больше трафика, чем тот готов сиюминутно пропустить.

Причины перегрузок

Самая простая — из высокоскоростного интерфейса трафик должен слиться в более низкоскоростной — из 10G в 1, например.

Другая причина, очень распространённая в сетях крупных ДЦ, особенно в тех, где развёрнуты кластеры Map-Reduce — это Incast. Это ситуация, в которой одна машина отправляет запрос на десятки/сотни/тысячи, а те все разом начинают отвечать, и пакеты стопорятся на узком интерфейсе в сторону машины-инициатора.

Более общий случай — трафик с нескольких входящих портов должен влиться в один исходящий — Backpressure.

Прочие типы всплесков трафика, которые ещё называют бёрстовыми или просто бёрстами (Bursts).

Поэтому однозначно нужно побольше памяти для буферизации. Но фактически это место, где пакеты обрастают задержкой.

Так на заре 1G буферизация вызывала массу головной боли у трейдеров, чьи приложения получали свой бесценный трафик с задержкой и джиттером.

И поэтому тут уже недостаточно везде FIFO. Это задача, во благо которой трудится QoS.

Если случилась конгестия, то нужно иметь возможность требовательный к задержкам трафик, пропустить первым, чувствительный к потерям — не дропнуть, а наименее ценным пожертвовать.

Ещё нужно уметь пополисить и пошейпить.

Но в каком месте располагать эту память и где реализовывать QoS?

Места возникновения перегрузок

Их по большому счёту 4:

- на входном чипе — если со стороны интерфейсов на него поступает больше, чем он способен обработать.

- на фабрике коммутации (если коробка модульная) — если линейные карты пытаются отправить на фабрику больше, чем она способна обработать.

- на выходной линейной карте, если фабрика пытается передать на линейную карту больше, чем её чип способен обработать

- на выходном интерфейсе — если чип шлёт в интерфейс больше, чем тот способен сериализовать.

Но никто не хочет бороться с перегрузками в четырёх местах.

Поэтому обычно

А) Чип делают такой производительности, чтобы он смог обработать весь трафик, даже если тот начал одновременно поступать со всех портов на этой линейной карте. Поэтому для устройства со 128 портами 100Гб/с используется чип с производительностью 12,8Тб/с.

Очевидно бывают и исключения. Тогда или имеем непредсказуемые потери, или (чаще) невозможность использовать часть портов.

Б) Фабрику так же делают без переподписки, чтобы она могла провернуть весь трафик, который пытаются в неё передать все линейные карты, даже если они делают это одновременно на полной скорости. Таким образом не нужно буферизировать трафик и перед отправкой на фабрику. Более того, её приходится делать не просто равной сумме пропускных способностей входных/выходных интерфейсов, а больше — там ведь помимо самих пакетов передаются ещё метаданные.

В) Управление перегрузками на выходном чипе и выходном интерфейсе сводят в одно место.

На самом деле фабрика без передподиски (или неблокируемая) — это та ещё спекуляция, к которой нередко прибегают маркетологи.

Для некоторых сценариев, например, CIOQ даже со speedup фабрики в пару раз от необходимого есть строгие результаты, показывающие, при каких условиях она будет неблокируемой.

Можно почитать у достопочтенных выпускников MIT и Стэнфорда: On the speedup required for combined input and output queued switching.

Архитектура буферов

И вот тут на сцену выходит TM — Traffic Manager, который реализует функции QoS (и некоторые другие).

Он может быть частью чипа коммутации, а может быть отдельной микросхемой — для нас сейчас важно то, что он заправляет буферами.

Буфер — это с некоторыми оговорками обычная память, используемая в компьютерах. В ней в определённой ячейке хранится пакет, который чип может извлечь, обратившись по адресу.

Любой сетевой ASIC или NP обладает некоторым объёмом встроенной (on-chip) памяти (порядка десятков МБ).

Так называемые Deep-Buffer свитчи имеют ещё внешнюю (off-chip) память, исчисляемую уже гигабайтами.

И той и другой управляет модуль чипа — MMU.

В целом для нас пока местонахождение не имеет значения — взглянем на это попозже. Важно то, как имеющейся памятью чип распоряжается, а именно, где и какие очереди он создаёт и какие AQM использует.

И тут практикуют:

- Crossbar

- Shared Buffer

- Output Queuing

- Input Queueing

- Combined Input and Output Queueing

- Virtual Output Queueing

Crossbar

Идея в том, чтобы для каждой пары (входной интерфейс — выходной интерфейс) выделить аппаратный буфер.

Это, скорее, умозрительный эксперимент, потому что в плане сложности, стоимости реализации и эффективности это проигрышный вариант.

Shared Buffer

По числу существующих в мире коробок этот вариант, однозначно, на первом месте.

Используется Shared Buffer на немодульных устройствах без фабрики коммутации, в которых установлен один чип (обычно, но может быть больше).

Аппаратно — это память (обычно SRAM), встроенная прямо в чип — она так и называется on-chip (OCB). Много туда не засунешь, поэтому объём до 100 МБ.

Зачастую это единственная память, которая в одночиповых устройствах используется для буферизации.

Пусть, однако, эта кажущаяся простота не вводит вас в заблуждение — для того, чтобы в десятки мегабайтов поместить трафик сотни портов 100Гб/с, да ещё и обеспечить отсутствие потерь, за ними должны скрываться годы разработок и нетривиальная архитектура.

А так оно и есть — я чуть ниже неглубоко вас окуну.

Итак, есть соблазн эту память взять и просто равномерно разделить между всеми портами. Такой статический дизайн имеет право на жизнь, но сводит на нет возможность динамически абсорбировать всплески трафика.

Гораздо более привлекательным выглядит следующий вариант:

Dedicated + Shared

Из доступной памяти каждому порту выделяется определённая небольшая часть — это Dedicated Buffer. За каждым портом кусочек памяти законодательно закреплён и не может быть использован другими портами. То есть при любых обстоятельствах у порта будет свой защищённый кусочек. Минимальный размер Dedicated Buffer где-то настраивается, где-то нет. Но лучше без основательного понимания в дефолты не лезть.

Доля каждого порта в абсолютных цифрах очень маленькая — порядка единиц кБ.

Гарантируемый минимум выделяется для хранения как входящих пакетов, так и выходящих.

Остальная часть памяти как раз общая — Shared Buffer — может быть использована любым портом по мере необходимости. Из неё динамически выделяются куски для тех интерфейсов, которые испытывают перегрузку.

Например, если чип пытается на один из интерфейсов передать больше трафика, чем тот способен отправлять в единицу времени, то эти пакеты сначала заполняют выделенный для этого порта буфер, а когда он заканчивается, автоматически начинают складываться в динамически выделенный буфер из общей памяти. Как только все пакеты обработаны, память освобождается.

Под общий буфер может быть отдано 100% той памяти, что осталась после вычитания из неё выделенных для портов кусочков (Dedicated). Но она так же может быть перераспределена — за счёт общего буфера можно увеличить выделенные. Так, если выделить 80% под Shared, то оставшиеся 20% равномерно распределятся по Dedicated.

Наличие Shared Buffer’а решает огромную проблему, позволяя сглаживать всплески трафика, когда перегрузку испытывает один или несколько интерфейсов.

Однако вместе с тем за общую память начинаются соревноваться разные порты одновременно. И серьёзная перегрузка на одном порту может вызвать потери на другом, которому нужно было всего лишь несколько килобайтов общей памяти, чтобы не дропнуть пакет.

Одним из способов облегчить эту ситуацию является увеличение выделенных буферов за счёт уменьшения общего.

Но это всегда зона компромиссных решений — сокращая размер общей памяти, мы уменьшаем и объёмы всплесков, которые чип может сгладить.

Кроме того Lossless трафик требует к себе ещё более щепетильного отношения.

Поэтому зачастую, помимо Dedicated и Shared буферов, резервируют ещё Headroom buffers.

Headroom buffers

Это последний способ сохранить пакеты, когда даже общий буфер уже забит. Естественно, он тоже отрезается от общей памяти, поэтому на первый взгляд выглядит не очень логичным откусить от общей памяти кусок, назвать его по-другому и сказать, мол, мы всё оптимизировали.

На самом деле Headroom буферы решают довольно специфическую задачу — помочь lossless приложениям с PFC — Priority-based Flow Control.

PFC — это механизм Ethernet Pause, который умеет притормаживать не всю отправку, а только по конкретным приоритетам Ethernet CoS.

Например, два приложения на отправителе: RoCE и репликация БД. Первое — чувствительная к задержкам и потерям вещь, второе — массивные данные.

Коммутатор, заметив заполнение общего буфера, отправляет Pause для более низкого приоритета, тем самым притормаживая репликацию, но не RoCE.

Задача буфера Headroom здесь в том, чтобы сохранить in-flight пакеты приоритетной очереди (те, что сейчас в кабеле), пока Pause летит к отправителю с просьбой притормозить.

То есть пакеты репликации начнут дропаться, когда заполнится общий буфер, а пакеты RoCE будут складываться в Headroom.

Помимо lossless headroom бывает и headroom для обычного трафика, чтобы помочь сохранить более приоритетный. Но это на домашнее задание.

При наступлении перегрузки буферы будут задействованы в следующем порядке.

Для входящего best-effort трафика:

- Dedicated buffers

- Shared buffers

Для входящего lossless трафика:

- Dedicated buffers

- Shared buffers

- Lossless headroom buffers

Для всего исходящего трафика:

- Dedicated buffers

- Shared buffers

Разумеется, описанное выше лишь частный пример, и от вендора к вендору ситуация может различаться (разительно).

Например бродкомовские чипы (как минимум Trident и Tomahawk) имеют внутреннее разделение памяти по группам портов. Общая память делится на порт-группы по 4-8 портов, которые имеют свой собственный кусочек общего буфера. Порты из одной группы, соответственно буферизируют пакеты только в своём кусочке памяти и не могут занимать другие. Это тоже один из способов снизить влияние перегруженных портов друг на друга. Такой подход иногда называют Segregated Buffer.

Admission Control

Admission Control — входной контроль — механизм, который следит за тем, можно ли пакет записывать в буфер. Он не является специфичным для Shared-буферов, просто в рамках статьи — это лучшее место, чтобы о нём рассказать.

Формально Admission Control делится на Ingress и Egress.

Задача Ingress Admission Control — во-первых, вообще убедиться, что в буфере есть место, а, во-вторых, обеспечить справедливое использование памяти.

Это означает, что у каждого порта и очереди всегда должен быть гарантированный минимальный буфер. А ещё несколько входных портов не оккупируют целиком весь буфер, записывая в него всё новые и новые пакеты.

Задача Egress Admission Control — помочь чипу абсорбировать всплески, не допустив того, чтобы один или несколько выходных портов забили целиком весь буфер, получая всё новые и новые пакеты с кучи входных портов.

В случае Shared Buffer оба механизма срабатывают в момент первичного помещения пакета в буфер. То есть никакой двойной буферизации и проверки не происходит.

Как именно понять, сколько буфера занято конкретным портом/очередью и главное, сколько ещё можно ему выдать?

Это может быть статический порог, одинаковый для всех портов, а может быть и динамически меняющийся, регулируемый параметром Alpha.

Alpha

Итак, почти во всех современных чипах память распределяется динамически на основе информации о том, сколько общей памяти вообще свободно и сколько ещё можно выделить для данного порта/очереди.

На самом деле минимальной единицей аккаунтинга является не порт/очередь, а регион (в терминологии Мелланокс). Регион — это кортеж: (входной порт, Priority Group на входном порту, выходной порт, Traffic Class на выходном порту).

Каждому региону назначается динамический порог, сколько памяти он может под себя подмять. При его превышении, очевидно, пакеты начинают дропаться, чтобы не влиять на другие регионы.

Этот порог вычисляется по формуле, множителями которой являются объём свободной на данный момент памяти и параметр alpha, специфичный для региона и настраиваемый:

Threshold [Bytes] = alpha * free_buffer [Bytes]Его значение варьируется от 1/128 до примерно 8 с шагом х2. Чем больше эта цифра, тем больший объём свободной памяти доступен региону.

Например, если на коммутаторе 32 региона, то:

при alpha=1/64 каждому региону будет доступна 1/64 часть свободной памяти, и даже при максимальной утилизации они все смогут использовать только половину буфера.

при alpha=1/32 вся память равномерно распределится между регионами, ни один из них не сможет влиять на другие, а при полной утилизации 100% памяти будет занято.

при alpha=1/16 каждый регион может претендовать на больший объём памяти. И если все регионы разом начнут потреблять место, то им всем не хватит, потому что памяти потребовалось бы 200%. То есть это своего рода переподписка, позволяющая сглаживать всплески.

Предполагаем тут, что значение alpha одинаково для всех регионов, хотя оно может быть настроено отдельно для каждого.

При получении каждого пакета, механизм Admission Control вычисляет актуальный порог для региона, которому принадлежит пакет. Если порог меньше размера пакета, тот отбрасывается.

Если же больше, то он помещается в буфер и уже не будет отброшен никогда, даже если регион исчерпал все лимиты. Объём свободной памяти уменьшается на размер пакета.

Это происходит для каждого приходящего на чип пакета.

Написанное выше об Admission Control и Alpha может быть справедливо не только для Shared Buffers, но и для других архитектур, например, VoQ.

Дальнейшее чтиво:

- Если в жизни не хватает страданий: Design and Implementation of a Shared Memory Switch Fabric

- Understanding the Alpha Parameter in the Buffer Configuration of Mellanox Spectrum Switches

- Programming Guide’ы коммерческих микросхем (NDA кровью, помним, да?).

Crossbar и Shared Buffer — это архитектуры, которые могут использоваться для устройств фиксированной конфигурации (возможно, даже multi-chip), но не подходят для модульных.

Взглянем же теперь на них.

Дело в том, что они состоят из нескольких линейных карт, каждая из которых несёт как минимум один самостоятельный чип коммутации.

И этот чип, будь то ASIC, NP или даже CPU не может в своей внутренней памяти динамически выделять буферы для тысяч очередей выходных интерфейсов — кишка тонка.

Далее поговорим про архитектуры памяти для модульных шасси:

Output Queueing

Наиболее логичным кажется буферизировать пакеты как можно ближе к месту возможного затора — около выходных интерфейсов.

Кому как не выходному чипу знать о здоровье своих подопечных интерфейсов, обслуживать по несколько QoS очередей для каждого и бороться с перегрузками?

И это правда так.

Но есть одна фундаментальная проблема — в случае перегрузок пакеты будут приходить на Egress PFE, чтобы умирать. Они проделают весь огромный путь от входного интерфейса через фабрику коммутации до выходного буфера через фабрику для того, чтобы узнать, что мест нет и быть печально дропнутыми.

Это бессмысленная и бесполезная утилизация полосы пропускания фабрики.

И вот уже вырисовывается следующая логичная мысль — выбросить пакет нужно как можно раньше.

Как было бы здорово, если бы мы могли это сделать на входной плате.

Input Queuing

Более удачным вариантом оказывается буферизировать пакеты на входной плате после лукапа, когда уже становится понятно, куда пакет слать. Если выходной интерфейс заведомо занят, то и смысла гнать камикадзе на фабрику нет.

Постойте! Как же входной чип узнает, что выходной интерфейс не занят?

С точки зрения Data Plane никакой обратной связи, от выходного чипа входному, очевидно, нет. Распространение между ними информации, необходимой для лукапа (некстхопы, интерфейсы, заголовки) производится средствами медленного Control Plane — тоже не подойдёт.

Так вот для сигнализации такой информации между линейными платами появляется арбитр. У разных вендоров он может быть реализован по-разному, но суть его в следующем — входной чип регулярно запрашивает у выходного разрешение на отправку нового блока данных. И пока он его не получит — держит пакеты в своём буфере, не отправляя их в фабрику.

Соответственно выходной чип, получив такой запрос, смотрит на утилизацию выходного интерфейса и решает, готов ли он принять пакет. Если да — отправляет разрешение (Grant).

Это на первый взгляд контринтуитивное поведение — каковы же накладные расходы на такой арбитраж, насколько это увеличивает задержки, если на отправку пакета данных нужно дождаться RTT в пределах коробки — пока запрос улетит на выходной чип, пока тот обработает, пока ответ вернётся назад.

Тут некоторые платформы оптимизируют: request/grant’ы присобачиваются к data-пакетам piggyback’ом.

Итога вместо data1 → request2 → data2 → request3 получается data1+request2 → data2+request3.

В любом случае тут для меня начинается область магического искусства, но вендоры эту революцию успели совершить и есть масса платформ, на которых арбитр прекрасно со своей задачей справляется.

Хотя обычно он применяется не для Input Queueing в описанном виде.

Дело в том, что эффективность Input Queueing не очень высокая — очень часто придётся ждать, пока интерфейс освободится. Эх, прям вспоминается старый добрый Ethernet CSMA/CD.

Combined Input and Output Queueing

Гораздо выгоднее в этом плане разрешить буферизацию и на выходе.

Тогда арбитр будет проверять не занятость интерфейса, а степень заполненности выходного буфера — вероятность, что в нём есть место, гораздо выше.

Но такие вещи не даются даром. Очевидно, это и увеличенная цена из-за необходимости реализовывать дважды буферизацию, и увеличенные задержки — даже в отсутствие заторов этот процесс не бесплатный по времени.

Кроме того, для обеспечения QoS придётся хоть какой-то минимум его функций реализовывать в двух местах, что опять же скажется на цене продукта

Но у CIOQ (как и у IQ) есть фундаментальный недостаток, заставивший в своё время немало поломать голову лучшим умам — Head of Line Blocking.

Представьте себе ситуацию: однополосная дорога, перекрёсток, машине нужно повернуть налево, сквозь встречный поток. Она останавливается, и ждёт, когда появится окно для поворота. А за ней стоит 17 машин, которым нужно проехать прямо. Им не мешает встречный поток, но им мешает машина, которая хочет повернуть налево.

Этот избитый пример иллюстрирует ситуацию HoLB. Входной буфер — один на всех. И если всего лишь один выходной интерфейс начинает испытывать затор, он блокирует полностью очередь отправки на выходном чипе, поскольку один пакет в начале этой очереди не получает разрешение на отправку на фабрику.

Трагическая история, как в реальной жизни, так и на сетевом оборудовании.

Virtual Output Queueing

Как можно исправить эту дорожную ситуацию? Например, сделав три полосы — одна налево, другая прямо, третья направо.

Ровно то же самое сделали разработчики сетевого оборудования.

Они взяли входной буфер побольше и подробили его на множество очередей.

Для каждого выходного интерфейса они создали по 8 очередей на каждом чипе коммутации. То есть перенесли все задачи по обеспечению QoS на входной чип. На выходном же при этом остаётся самая базовая FIFO очередь, в которой никогда не будет заторов, потому что их контроль взял себя входной чип.

Если взять грубо коробку со 100 интерфейсами, то на каждой плате в буферах нужно будет выделить 800 очередей.

Если в коробке всего 10 линейных карт, то общее число очередей на ней будет 100*8*10 = 8000.

Однако V в VOQ означает виртуальный, не потому, что они как бы выходные, но на самом деле находятся на входных платах, а потому что Output Queue для каждого выходного интерфейса распределён между всеми линейными картами. То есть сумма 10и физических очередей для одного интерфейса на 10 чипах составляет 1 виртуальную.

Собственно из-за распределённого характера этой виртуальной очереди от арбитра и здесь избавиться не получится — разным входным чипам всё же нужно знать, состояние выходной очереди. Поэтому даже несмотря на то, что выходная очередь — это FIFO, выходной чип всё ещё должен давать добро на отправку трафика.

Кстати, что касается трафика, который должен вернуться в интерфейс той же карты, на которую он пришёл изначально, то здесь никаких исключений — он томится в VOQ, пока чип не даст добро переложить его в выходную очередь. С тем только отличием, что пакет не будет отправляться на фабрику. Поэтому перед лицом перегрузок все равны.

На сегодняшний день End-to-End VOQ является наиболее прогрессивной технологией, но говорить о её безоговорочной победе пока не приходится.

Картинка с NANOG65 (2015):

Дальнейшее чтиво:

- An Update on Router Buffering

- What is VOQ and why you should care?

- Strategies of packet buffering inside Routers

- Understanding CoS Virtual Output Queues (VOQs) on QFX10000 Switches

- High Performance Switches and Routers — если у вас есть лишних 14 к₽.

Shallow vs Deep Buffers

Буферы — это то место, где пакеты можно похранить, вкачав в них смертельную порцию задержки.

Как сказали в видео Packet Pushers — буферы — это религия. Хотя, скорее всего, неортодоксальная, а возможно даже секта.

Чуть позже мы поговорим о том, что такое хорошо, а что такое плохо. А пока посмотрим на реализации.

Shallow — неглубокие — это буферы размером до 100МБ. Обычно это встроенная в кристалл on-chip память — OCB — On-Chip Buffer.

Deep — счёт уже идёт на гигабайты. Обычно off-chip и подключается к чипу по отдельной шине.

И нет ничего посередине.

За последние лет десять производительность чипов выросла на порядки, трафика они теперь перемалывают терабиты в секунду вместо единиц гигабит. А размер памяти не то что не поспевает за этим ростом, он фактически почти стоит на месте.

Давайте грубо прикинем: если для гигабитного порта буфер размером 16 мегабайт мог абсорбировать всплеск трафика длительностью примерно 100 мс, то для 100Гб/с — всего лишь 1мс. И это только один порт, фактически же плотность портов тоже растёт и максимальная комплектация для одночипового устройства сегодня — 64 порта 400Гб/с — или 25,6 Тб/с полосы пропускания.

Используя только 64 МБ буфер, такой чип сможет хранить трафик 0.000005 c или 5 мкс.

Такие буферы порой даже называют Extremely shallow buffers.

Их воистину миниатюрный объём обусловлен в первую очередь тем, что они в прямом смысле встроены в чип. Такая память является составной частью микросхемы, и каждый дополнительный мегабайт, разумеется, будет обходиться в лишнюю тысячу долларов, больший размер и тепловыделение. Для справки Broadcom Trident 4 содержит 21 миллиард транзисторов, изготовленных по 7нм техпроцессу (это меньше размера капсида любого существующего вируса) на нескольких квадратных сантиметрах.

Логично вытекающим следствием является скорость работы с этой памятью — она должна соответствовать производительности чипа.

Очевидно, что не для всех задач такие маленькие буферы подходят. В частности модульные коробки с VOQ явно не могут позволить себе дробить 64 Мб на несколько тысяч очередей (на самом деле могут).

Поэтому рынок предлагает решения с большой внешней памятью (Deep Buffers), размер которой начинается от 1ГБ (обычно от 4ГБ).

Согласно этой таблице существуют коммутаторы (Arista 7280QR-C48) с фантастическими 32-хгигабайтовыми буферами — это уже все сезоны Рика и Морти в неплохом качестве. Но это уже история про VOQ — всё-таки это память не одного чипа. На моём первом ПК такого объёма был жёсткий диск.

Как такая память реализована зависит уже от чипа и коробки.